**Border Traps**

# Al<sub>2</sub>O<sub>3</sub> Insertion Layer for Improved PEALD SiO<sub>2</sub>/(Al)GaN Interfaces

Jianyi Gao,\* Mei Hao, Wenwen Li, Zheng Xu, Saptarshi Mandal, Robert Nemanich, and Srabanti Chowdhury

The development of high-quality gate dielectric/III-N semiconductor interfaces is indispensable to achieve high performance GaN-based high electron mobility transistors (HEMTs). In this work, we present improved interfaces between SiO<sub>2</sub> and GaN (or AlGaN) with Al<sub>2</sub>O<sub>3</sub> insertion layer deposited by plasma-enhanced atomic layer deposition (PEALD). Interface state density (D<sub>it</sub>) and border trap density (N<sub>bt</sub>) were characterized using UV-assisted C–V measurement on metal-oxide-semiconductor capacitors (MOSCAPs). SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> insertion layer exhibited integrated D<sub>it</sub> of 1.93  $\times$  10<sup>11</sup> cm<sup>-2</sup>, one order of magnitude lower than that without Al<sub>2</sub>O<sub>3</sub> insertion layer. N<sub>bt</sub> of SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> insertion layer is nearly twice of that without Al<sub>2</sub>O<sub>3</sub> insertion layer. Stressed C–V measurement further confirmed improved interface with Al<sub>2</sub>O<sub>3</sub> insertion layer. To investigate the performance of MOS-HEMT using SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> insertion layer as a gate dielectric, pulsed I<sub>DS</sub>–V<sub>GS</sub> measurements were performed. MOS-HEMT exhibited positive threshold voltage shift, which is attributed to electron trapping in interface states and border traps.

## 1. Introduction

GaN based high electron mobility transistors (HEMTs) are of particular interest for high-power switching applications owing to their superior physical properties such as high breakdown field and high electron mobility. [1,2] Metal-oxide-semiconductor (MOS) structures are preferred over conventional Schottky gates since they provide suppression of gate leakage, large operating voltage and the ability to achieve normally off operation. [3,4] However, deposition of foreign dielectrics on GaN results in the formation of a high-density of interface states ( $D_{it} \approx 10^{12} - 10^{13} \, \text{eV}^{-1} \, \text{cm}^{-2})^{[5]}$  due to incomplete chemical bonds, structural damage and impurities at the dielectric/GaN interface. The interface states with both short and long emission time constants, are in electrical communication with the underlying semiconductor. Interface

J. Gao, W. Li, Z. Xu, Dr. S. Mandal, Prof. S. Chowdhury Department of Electrical and Computer Engineering University of California Davis, CA 95616, USA

E-mail: jiagao@ucdavis.edu M. Hao, Prof. R. Nemanich Department of Physics Arizona State University Tempe, AZ 85281, USA

DOI: 10.1002/pssa.201700498

states can be charged and discharged depending on the surface potential and thus result in the threshold voltage instability of MOS-HEMTs. [6–8] Therefore, the development of high-quality gate dielectric/III-N interfaces plays perhaps the most significant role in achievement of high performance MOS-HEMTs.

Various oxide materials have been reported as gate dielectric for GaN MOS-HEMTs. For example, Si<sub>3</sub>N<sub>4</sub> deposited by in situ metalorganic chemical vapor deposition (MOCVD),[9] Al<sub>2</sub>O<sub>3</sub> deposited by MOCVD<sup>[10]</sup> or atomic layer deposition (ALD),[11-13] HfO<sub>2</sub> deposited by ALD[14,15] and SiO<sub>2</sub> deposited by ALD<sup>[16]</sup> or plasma enhanced chemical vapor deposition.<sup>[17]</sup> Among these, Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> have been two of the most suitable oxides owing to their relatively large conduction band offset (CBO) with GaN and large breakdown electric field. However, the CBO of Al<sub>2</sub>O<sub>3</sub>  $(\approx 2.13 \text{ eV})^{[18]}$  is smaller than that of SiO<sub>2</sub>  $(\approx 3.6 \,\mathrm{eV})$ , <sup>[19]</sup> resulting in considerable gate

leakage current. On the other hand, the interface state density  $(D_{it})$  of  $SiO_2/GaN$  is larger than  $Al_2O_3/GaN$ , resulting in a severe threshold voltage instability. Composite gate dielectric has been proposed to overcome the disadvantage given by a single dielectric. For example, Kambayashi et al.  $^{[20]}$  showed a gate stack consisting of ALD  $Al_2O_3$  and MW-PECVD  $SiO_2$  with high breakdown field and low interface state density. Kikuta et al.  $^{[21]}$  reported  $Al_2O_3/SiO_2$  nanolaminate with different ratio of  $Al_2O_3$  to  $SiO_2$  for a gate dielectric in GaN-based transistors.

In this paper, improved interfaces between plasma enhanced ALD (PEALD)  $SiO_2$  and GaN (or AlGaN) are demonstrated, with an  $Al_2O_3$  insertion layer.  $D_{it}$  and  $N_{bt}$  were characterized using UV-assisted C-V measurement on MOSCAPs. Pulsed  $I_{DS}$ -V $_{GS}$  measurements were performed on MOS-HEMT to evaluate threshold voltage shifts related to interface states with long emission times and border traps.

## 2. Experimental Section

## 2.1. MOSCAP

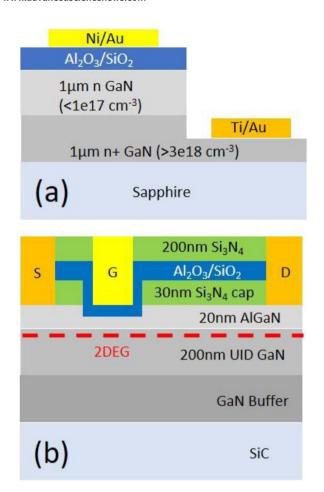

The GaN epilayer was grown on 2-inch diameter sapphire substrate by MOCVD. The layer structure, shown in Figure 1(a)

Figure 1. Schematic diagram of (a) PEALD  $Al_2O_3/SiO_2$  MOSCAP and (b) AlGaN/GaN MOS-HEMT.

consists of  $1 \,\mu m \, n^+$  GaN with doping of  $\approx 3 \times 10^{18} \, cm^{-3}$  and  $1 \,\mu m$  n GaN with doping of  $\approx 1 \times 10^{17} \, cm^{-3}$ . Following a standard solvent clean of the sample, in situ N<sub>2</sub>/H<sub>2</sub> plasma pretreatment in the PEALD chamber was carried out prior to the dielectric deposition. The sample was annealed at 400 °C in N2 ambient for 15 min after the plasma pretreatment to alleviate the surface damage. Twenty cycles of Al<sub>2</sub>O<sub>3</sub> deposition was performed using dimethylaluminum isopropoxide (DMAI) and O2 as precursors, followed by 200 cycles of SiO2 deposition using tris(dimethylamino)silane (TDMAS) and O2 plasma as precursors at room temperature. The thickness of Al<sub>2</sub>O<sub>3</sub> and  $SiO_2$  was determined to be  $\approx$ 2 and 20 nm respectively, from the product of the number of deposition cycles and the foreknown deposition rate which were 1.1 and 1.0 A/cycle for Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> respectively. In situ X-ray photoelectron spectroscopy (XPS) analysis was conducted after the deposition of the insertion and bulk layers. The sample was annealed, post-deposition, in N2 ambient at 400 °C for 15 min. MOSCAP shown in Figure 1 with diameter of 200 µm was fabricated with the following steps. Mesa isolation consisted of CHF<sub>3</sub>/Ar (25 sccm/25 sccm) RIE to etch SiO<sub>2</sub> and BCl<sub>3</sub>/Cl<sub>2</sub>/Ar (8 sccm/30 sccm/5 sccm) ICP to etch GaN. Then, gate contacts consisting of Ni/Au (20 nm/200 nm) were formed on the oxides by e-beam evaporation and lift-off process. Finally, Ohmic contacts consisting of Ti/Au ( $20\,\text{nm}$ /  $200\,\text{nm}$ ) were formed on the  $\text{n}^+$  GaN. The  $\text{SiO}_2/\text{GaN}$  MOSCAP without  $\text{Al}_2\text{O}_3$  insertion layer was prepared for comparison. The thickness of  $\text{SiO}_2$  was  $22\,\text{nm}$  to maintain the same physical oxide thickness with the MOSCAP with  $\text{Al}_2\text{O}_3$  insertion layer.

#### 2.2. MOS-HEMT

The device schematic of the AlGaN/GaN MOS-HEMT is depicted in Figure 1. MOCVD grown AlGaN/GaN HEMT structures consisted of 30 nm Si<sub>3</sub>N<sub>4</sub> cap layer, 20 nm Al<sub>0.25</sub>Ga<sub>0.75</sub>N, 200 nm UID GaN, and Fe-doped GaN buffer layer on SiC substrate. Mesa isolation was performed by CHF<sub>3</sub>/ O2 RIE to etch Si3N4 and BCl3/Cl2 ICP to etch AlGaN/GaN. Source/drain Ohmic contacts consisting of Ti/Al/Ni/Au were formed by e-beam deposition and a lift-off process on the AlGaN layer, which was then annealed at 860 °C for 30 s in an N2 ambient. PEALD SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> insertion layer were then deposited as gate dielectric. Gate contacts consisting of Ni/Au/Ni were defined using a lift-off process. 200 nm PECVD Si<sub>3</sub>N<sub>4</sub> was deposited as a passivation layer. Finally, source, drain and gate vias were formed. The fabricated MOS-HEMT features a gate length of 1 µm, a gate to source distance of 2 µm and a gate to drain distance of 6 µm. The gate width is 50 µm.

## 3. Physical Characterization

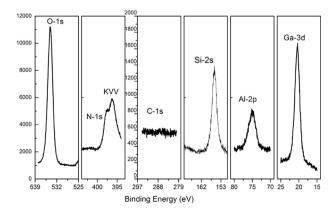

Figure 2 shows the combined element profile of the insertion oxide layer and bulk oxide layer analyzed by XPS. Al 2p core-level spectrum was determined near the interface and Si 2s core-level spectrum was determined in the bulk. It indicates that the oxide consists of  $Al_2O_3$  insertion layer and  $SiO_2$  bulk layer.

#### 4. Electrical Characterization

## 4.1. Forward I-V Measurement

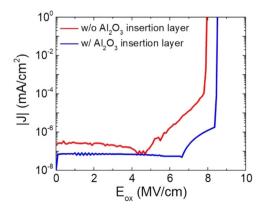

Breakdown field ( $E_{\rm br}$ ) was characterized by forward-biased I–V measurements on MOSCAPs using a Keithley 4200-SCS parameter analyser with a sweep rate of 0.56 V s $^{-1}$ . The electric

Figure 2. Element profile of the oxide thin film on GaN analyzed by XPS.

field across the oxide is determined by the gate voltage over the equivalent oxide thickness ( $E_{\rm OT}$ ) in terms of SiO<sub>2</sub>.  $E_{\rm OT}$  can be calculated using the following equation:  $E_{\rm OT} = t_{\rm SiO2} + t_{\rm Al2O3} \frac{k_{\rm SiO2}}{k_{\rm Al2O3}}$ . **Figure 3** shows current density-electric field characteristics of MOSCAP with and without Al<sub>2</sub>O<sub>3</sub> insertion layer. The  $E_{\rm br}$  of MOSCAP with Al<sub>2</sub>O<sub>3</sub> insertion layer (8.5 MV cm<sup>-1</sup>) is slightly higher than that of MOSCAP without Al<sub>2</sub>O<sub>3</sub> insertion layer (8.0 MV cm<sup>-1</sup>) because  $E_{\rm OT}$  for MOSCAP with Al<sub>2</sub>O<sub>3</sub> insertion layer, 20.88 nm is slightly lower than that for MOSCAP without Al<sub>2</sub>O<sub>3</sub> insertion layer, 22 nm.

#### 4.2. UV-assisted C-V Measurement

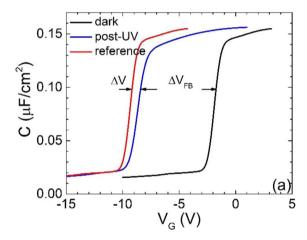

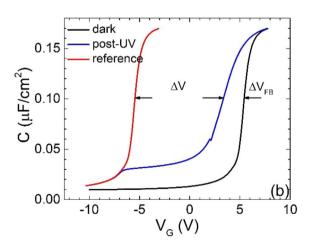

D<sub>it</sub> was characterized using UV-assisted C-V measurement, [22] with a modified Terman method for wide bandgap semiconductors. Although the conductance method has been widely used to evaluate the interface state density, [23,24] it can only measure interface states with short emission times and hence underestimates the interface state density in GaN devices due to the lack of hole generation. UV-assisted C-V measurements based on UV illumination to generate electron-hole pairs is preferred as the method gives more accurate detail of the interface state density as a function of energy. C-V characteristics were measured using a Keithley 4200-SCS parameter analyser at 1 MHz frequency, 80 mV s<sup>-1</sup> sweep rate and 30 mV amplitude AC signal. An OmniCure 1500 spot curing system with UV intensity peaks at 365, 400, and 430 nm wavelength was used as the UV illumination source. The energy of 365 nm UV is equivalent to  $\approx$ 3.41 eV, corresponding to the GaN bandgap. Figure 4 shows UV-assisted C-V measurement data for the MOSCAP. First, the MOSCAP was held in accumulation for 10 min to eliminate the initial variation in occupancy of interface states. Then a dark C-V curve was obtained by sweeping the MOSCAP from depletion to accumulation under the dark condition. Next, the MOSCAP was exposed to UV in depletion for 30 s to neutralize the filled interface states. It was then held in depletion for an additional 10 min after turning off the UV to let free holes leave the MOSCAP. Finally, post-UV curve was obtained by sweeping the device from depletion to accumulation under dark condition. A reference curve was

Figure 3. Current density-electric field characteristics of 200  $\mu m$  diameter MOSCAP with and without Al<sub>2</sub>O<sub>3</sub> insertion layer.

obtained by overlapping the depletion portion of the dark curve to that of the post-UV curve.

The voltage difference between the post-UV curve and reference curve ( $\Delta V$ ) at a given capacitance, determines the trapped interface states (the states that exist above the Fermi level). The change in  $\Delta V$  thus corresponds to the change in the occupancy of interface states due to the change in Fermi level. The position of the Fermi level is related to the surface potential ( $\psi_s$ ). Hence,  $D_{it}$  as a function of energy level can be determined by

$$D_{it} = \frac{C_{ox}}{q} \frac{d\Delta V}{d\Psi_s} \tag{1}$$

where  $C_{ox}$  is the oxide capacitance.

The flatband voltage shift ( $\Delta V_{FB}$ ) is associated with traps that are disconnected from the Fermi level since the existence of depletion region prevents bulk electrons in GaN from being trapped. These traps can only be occupied when the MOSCAP is in accumulation. These traps are located near the interface within the oxide, usually called border traps.<sup>[25]</sup> The amount of

**Figure 4.** UV-assisted C–V measurement data for  $SiO_2/GaN$  MOSCAP (a)  $w/Al_2O_3$  insertion layer and (b) w/o  $Al_2O_3$  insertion layer.

border traps (N<sub>bt</sub>) can be obtained by

$$N_{bt} = \frac{C_{ox}\Delta V_{FB}}{q} \tag{2}$$

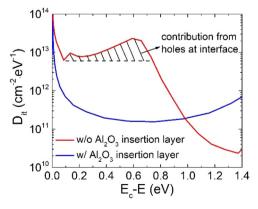

Figure 5 plots D<sub>it</sub> of SiO<sub>2</sub> with and without the Al<sub>2</sub>O<sub>3</sub> insertion layer as a function of energy level calculated from Eq. (1). There is a peak in the D<sub>it</sub> curve for SiO<sub>2</sub> without Al<sub>2</sub>O<sub>3</sub> insertion layer. Yeluri et al. [26] pointed out that the peak is attributed to the holes at the interface, in the case of material like SiO2 with a positive valence band offset to GaN (≈2 eV). [19] The valence band barrier at the interface prevents holes from leaving the system, affecting the measurement. The contribution of holes to the measurement corresponds to the shadow area under the peak as shown in Figure 5. On the other hand, there is no peak in the D<sub>it</sub> curve for SiO<sub>2</sub> with an Al<sub>2</sub>O<sub>3</sub> insertion layer. A possible explanation is that the Al<sub>2</sub>O<sub>3</sub> insertion layer assists holes with tunneling through the valence band barrier. When the MOSCAP is under negative bias condition, holes first direct tunnel (DT) through Al<sub>2</sub>O<sub>3</sub> insertion layer and subsequently reach the valence band of SiO<sub>2</sub> by trap-assisted tunneling (TAT). Such combination of DT and TAT mechanism was reported by Bhuyian et al. for a high-k dielectric with an interfacial layer.<sup>[27]</sup>

SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> insertion layer has much lower D<sub>it</sub> than SiO<sub>2</sub> without Al<sub>2</sub>O<sub>3</sub> insertion layer near the conduction band. Table 1 lists  $D_{it}$  integrated from  $E_c$ – $E=0.15\,eV$  to  $E_c$ – $E=1\,eV$ . The integrated Dit for SiO2 with and without Al2O3 insertion layer are  $1.93 \times 10^{11}$  and  $3.83 \times 10^{12}$  cm<sup>-2</sup> respectively. D<sub>it</sub> decreased by one order of magnitude with the presence of an Al<sub>2</sub>O<sub>3</sub> insertion layer. The values of N<sub>bt</sub> calculated from Eq. (2) are summarized in Table 1. N<sub>bt</sub> of SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> insertion layer is nearly twice that of SiO<sub>2</sub> without Al<sub>2</sub>O<sub>3</sub> insertion layer.

#### 4.3. Stressed C-V Measurement

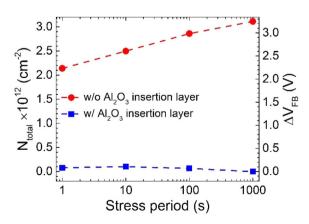

The MOSCAP was swept from depletion to accumulation, followed by the constant DC bias stress (4 V). After the stress, the accumulation to depletion curve was recorded for changes in the flatband voltage ( $\Delta V_{FR}$ ) with respect to the virgin depletion to accumulation curve. The same procedure was repeated for

Figure 5. Dit as a function of energy level.

Table 1. Dit and Nbt of SiO<sub>2</sub> with and without Al<sub>2</sub>O<sub>3</sub> insertion layer.

| SiO <sub>2</sub>                   | Integrated $D_{it}$ over 0.15 to 1 eV (cm $^{-2}$ ) | N <sub>bt</sub> (cm <sup>-2</sup> ) |

|------------------------------------|-----------------------------------------------------|-------------------------------------|

| w/o Al <sub>2</sub> O <sub>3</sub> | 3.83 × 10 <sup>12</sup>                             | 3.39 × 10 <sup>12</sup>             |

| w/Al <sub>2</sub> O <sub>3</sub>   | $1.93 \times 10^{11}$                               | $6.63 \times 10^{12}$               |

different stress period. Figure 6 plots  $\Delta V_{FB}$  as a function of stress period for SiO<sub>2</sub> with and without Al<sub>2</sub>O<sub>3</sub> insertion layer.  $\Delta V_{FB}$  is a measure of total net added charge ( $N_{total}$ ) during the stress.  $\Delta V_{FB}$ for SiO<sub>2</sub> without Al<sub>2</sub>O<sub>3</sub> insertion layer increases significantly with the increase of stress period. Corresponding  $N_{\text{total}}$  is  $pprox 3.0 \times 10^{12} \, \text{cm}^{-2}$  when stress period is  $1000 \, \text{s}$ . On the other hand, ΔV<sub>FB</sub> for SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> insertion layer is independent on stress period. Corresponding  $N_{total}$  is  $\approx 1.0 \times 10^{11} \, cm^{-2}$ . The value of N<sub>total</sub> is very closed to D<sub>it</sub> for both dielectrics, implying that total net added charge is dominated by charging of interface states. Stressed C-V measurement also reveals that improved interface is obtained with Al<sub>2</sub>O<sub>3</sub> insertion layer.

## 4.4. Pulsed IDS-VGS Measurement

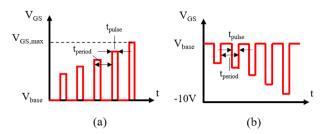

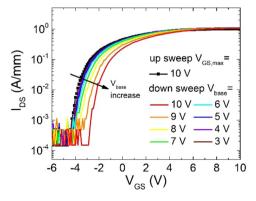

While D<sub>it</sub> and N<sub>bt</sub> can be quickly obtained by analysing the MOSCAP, it does not provide a direct indication of the effect on the performance of an actual MOS-HEMT. Pulsed I<sub>DS</sub>-V<sub>GS</sub> measurements have been used for interface state and border traps analysis in AlGaN/GaN MOS-HEMT.[28,29] In this work, the same method was conducted on AlGaN/GaN MOS-HEMT shown in Figure 1. The measurement features a constant drain bias ( $V_{DS} = 10 \text{ V}$ ) and a set of pulsed gate bias consisting of both low-base up-sweep and high-base down-sweep. The up-sweep and down-sweep waveforms applied at the gate are shown in **Figure 7**. The pulse width and pulse period are  $5 \mu s$  and 100 ms. In the up-sweep measurements, the base voltage  $(V_{base})$  is held at  $-10 \, \text{V}$ , much lower than  $V_t$ , to avoid electrons spill-over. [24] The pulse amplitude was gradually increased from V<sub>base</sub> to maximum gate bias ( $V_{GS,max} = 10 \text{ V}$ ) in steps of 0.1 V. The interface states are intended to be empty during the up-sweep measurements since the electron trapping is minimized by

Figure 6.  $N_{total}$  and  $\Delta V_{FB}$  as a function of stress period.

**Figure 7.** Waveform of  $V_{GS}$  during pulsed  $I_{DS}$ - $V_{GS}$  measurement: (a) low-base up-sweep and (b) high-base down-sweep.

short pulse and long period. In the down-sweep measurements,  $V_{\rm base}$  is held at high voltage, from 3 to 10 V. The pulse height is gradually decreased from  $V_{\rm base}$  to -10 V in steps of  $-0.1 \, V$ . The interface states below the Fermi level with emission time constant longer than the pulse width are filled in the down-sweep measurements. A certain amount of border traps is inevitably filled by electron spill-over in the meantime. Therefore, the threshold voltage difference between up-sweep and down-sweep  $(\Delta V_t)$  is attributed to the interface states with emission time constants longer than the pulse width as well as border traps.

The corresponding total traps (N<sub>total</sub>) can be calculated by

$$N_{\text{total}} = N_{bt} + D_{it} = \frac{C_{ox}\Delta V_t}{q}$$

(3)

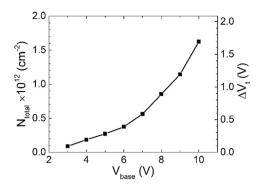

Figure 8 shows pulsed  $I_{DS}$ - $V_{GS}$  characteristics of AlGaN/GaN MOS-HEMT. Figure 9 plots  $N_{total}$  and  $\Delta V_t$  versus  $V_{base}$  of the down-sweep calculated from Eq. (3). Increasing  $\Delta V_t$  is due to the increasing amount of electron trapping in interface states and border traps as  $V_{base}$  increases. It should be noted that the pulsed  $I_{DS}$ - $V_{GS}$  measurement neither maps  $D_{it}$  as a function of energy level nor distinguishes interface states from border traps, unlike the UV-assisted C-V measurement. It evaluates the threshold voltage shift related to the combination of interface states and border traps within a certain detectable energy range, which is given by Shockley-Read-Hall statistics

Figure 8. Pulsed I<sub>DS</sub>-V<sub>GS</sub> measurement on AlGaN/GaN MOS-HEMT.

Figure 9.  $N_{total}$  versus  $V_{base}$  in the down-sweep measurement.

$$\tau = \frac{1}{\nu_{th}\sigma_n N_c} \exp\left(\frac{E - E_c}{kT}\right) \tag{4}$$

where  $v_{th}$ ,  $\sigma_n$  and  $N_c$  are electron thermal velocity, electron capture cross section and density of states in the conduction band in GaN, respectively.<sup>[30]</sup> The detectable energy range is calculated to be  $E_c$ – $E \ge 0.38$  eV.

#### 5. Conclusion

Improved interfaces between  $SiO_2$  and GaN (or AlGaN) have been obtained with an  $Al_2O_3$  insertion layer. XPS revealed that the oxide consists of an  $Al_2O_3$  insertion layer near interface and  $SiO_2$  in the bulk. Forward I–V measurement and UV-assisted C–V measurements were performed on PEALD  $SiO_2/GaN$  MOS-CAP to characterize the  $E_{\rm bp}$   $D_{\rm it}$  and  $N_{\rm bt}$ .  $D_{\rm it}$  decreased by one order of magnitude with the insertion of  $Al_2O_3$  layer.  $N_{\rm bt}$  increased by 2×. Stressed C–V measurements also confirmed improved interface for  $SiO_2$  with  $Al_2O_3$  insertion layer. Pulsed  $I_{DS}$ – $V_{GS}$  measurements were performed on AlGaN/GaN MOS-HEMTs to evaluate threshold voltage shifts related to interface states with long emission times and border traps. MOS-HEMTs exhibited positive  $\Delta V_{\rm tp}$  attributing to electron trapping in interface states and border traps.

#### Acknowledgement

The authors would like to thank ARPA-E for their continued support.

## **Conflict of Interest**

The authors declare no conflict of interest.

## Keywords

Al<sub>2</sub>O<sub>3</sub>, border traps, GaN, insertion layers, interface state density, SiO<sub>2</sub>

Received: July 18, 2017 Revised: October 21, 2017 Published online: January 10, 2018

#### www.advancedsciencenews.com

- [1] S. Chowdhury, Phys. Status Solidi A 2015, 212, 1066.

- [2] D. Ji, Y. Yue, J. Gao, S. Chowdhury, IEEE Trans. Electron Devices 2016, 63, 4011.

- [3] R. Chu, A. Corrion, M. Chen, R. Li, D. Wong, D. Zehnder, B. Hughes, K. Boutros, *IEEE Electron Device Lett.* 2011, 32, 632.

- [4] T. Huang, P. S. Park, S. Krishnamoorthy, D. N. Nath, S. Rajan, IEEE Electron Device Lett. 2014, 35, 312.

- [5] A. M. Sonnet, C. L. Hinkle, D. Heh, G. Bersuker, E. M. Vogel, IEEE Trans. Electron Devices 2010, 57, 2599.

- [6] S. Huang, S. Yang, J. Roberts, K. J. Chen, Jpn. J. Appl. Phys. 2011, 50, 11R.

- [7] P. Lagger, C. Ostermaier, D. Pogany, in: IEEE International Reliability Physics Symposium, Waikoloa, USA, **2014**, pp. 6C.3.1–6C.3.6.

- [8] H. A. Shih, M. Kudo, T. Suzuki, Appl. Phys. Lett. 2012, 101, 043501.

- [9] Y. Dora, A. Chakraborty, L. McCarthy, S. Keller, S. P. DenBaars, U. K. Mishra, IEEE Electron Device Lett. 2006, 27, 713.

- [10] D. Gregušová, R. Stoklas, K. Čícŏ, T. Lalinský, P. Kordoš, Semicond. Sci. Technol. 2007, 22, 947.

- [11] S. Huang, X. Liu, J. Zhang, K. Wei, G. Liu, X. Wang, Y. Zheng, H. Liu, Z. Jin, C. Zhao, C. Liu, S. Liu, S. Yang, J. Zhang, Y. Hao, K. J. Chen, IEEE Electron Device Lett. 2015, 36, 754.

- [12] B. Lu, T. Palacios, IEEE Electron Device Lett. 2013, 34, 369.

- [13] M. Ťapajnaa, L. Válik, F. Gucmann, D. Gregušová, K. Fröhlich, Š. Hašcík, E. Dobrocka, J. Vac. Sci. Technol. B 2017, 35, 01A107.

- [14] Y. Yue, Y. Hao, J. Zhang, J. Ni, W. Mao, Q. Feng, L. Liu, IEEE Electron Device Lett. 2008, 29, 838.

- [15] C. Liu, E. F. Chor, L. S. Tan, Semicond. Sci. Technol. 2007, 22, 522.

- [16] N. Ramanan, B. Lee, V. Misra, Semicond. Sci. Technol. 2015, 30, 125017.

- [17] M. A. Khan, X. Hu, G. Sumin, A. Lunev, J. Yang, R. Gaska, M. S. Shur, IEEE Electron Device Lett. 2000, 21, 63.

- [18] R. D. Long, P. C. McIntyre, Materials 2012, 5, 1297.

- [19] T. E. Cook, C. C. Fulton, W. J. Mecouch, K. M. Tracy, R. F. Davis, E. H. Hurt, G. Lucovsky, R. J. Nemanich, J. Appl. Phys. 2003, 93, 3995.

- [20] H. Kambayashi, T. Nomura, H. Ueda, K. Harada, Y. Morozumi, K. Hasebe, A. Teramoto, S. Sugawa, T. Ohmi, Jpn. J. Appl. Phys. 2013, 52, 04CF09.

- [21] D. Kikuta, K. Itoh, T. Narita, T. Mori, J. Vac. Sci. Technol. A 2017, 35, 01B122.

- [22] B. L. Swenson, U. K. Mishra, Appl. Phys. Lett. 2009, 106, 064902.

- [23] D. Gregušová, D. Gregušová, R. Stoklas, C. H. Mizue, Y. Hori, J. Novák, T. Hashizume, P. Kordoš, J. Appl. Phys. 2010, 107, 106104.

- [24] J. J. Freedsman, T. Kubo, T. Egawa, Appl. Phys. Lett. 2011, 99, 033504.

- [25] D. M. Fleetwood, IEEE Trans. Nucl. Sci. 1992, 39, 269.

- [26] R. Yeluri, X. Liu, B. L. Swenson, J. Lu, S. Keller, U. K. Mishra, J. Appl. Phys. 2013, 114, 083718.

- [27] M. N. Bhuyian, D. Misra, K. Tapily, R. D. Clark, S. Consiglio, C. S. Wajda, G. Nakamura, G. J. Leusink, ECS J. Solid State Sci. Technol. 2014, 3, N83.

- [28] X. Lu, K. Yu, H. Jiang, A. Zhang, K. M. Lau, IEEE Trans. Electron Devices 2017, 64, 824.

- [29] Y. Lu, S. Yang, Q. Jiang, Z. Tang, B. Li, K. J. Chen, Phys. Status Solidi C 2013, 10, 1397.

- [30] C. Mizue, Y. Hori, M. Miczek, T. Hashizume, Jpn. J. Appl. Phys. 2011, 50. 021001.